# 智能硬件体系结构

第九讲: MIPS架构与缓存设计

主讲: 陶耀宇、李萌

2025年秋季

< 2 >

#### ・课程作业情况

· 第2次lab时间: 11月14日-12月10日晚23:59

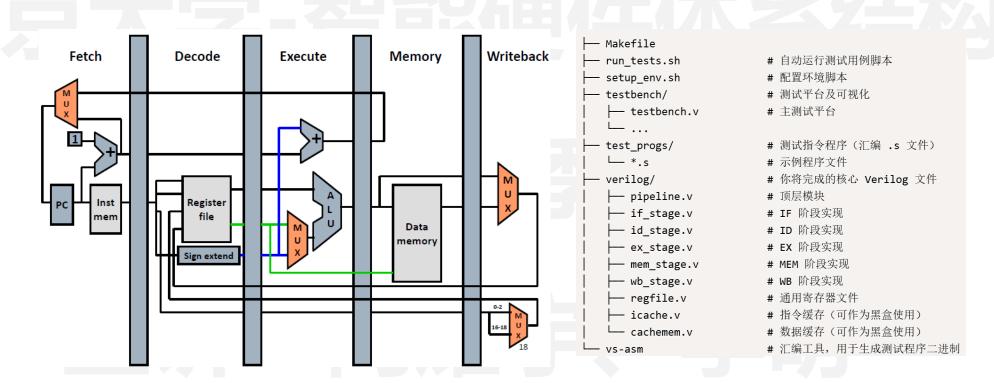

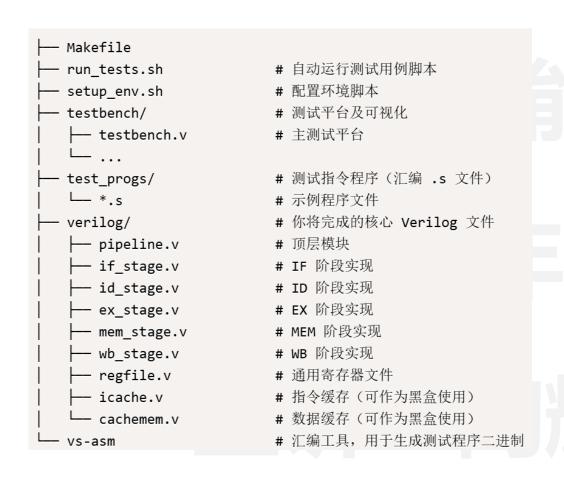

· Lab2的目标: 1、进一步熟悉硬件设计、验证与优化流程; 2、了解流水线的基本运行模式

#### ・课程作业情况

1. if\_stage.v ~5行代码 2. id\_stage.v // 在此处插入你的代码 ~15行代码 // 这里有任务详情的注释 // Insert your code below 3. ex\_stage.v ~15行代码 ... Your code here ... 4. mem\_stage.v // Insert your code above <5行代码 5. wb\_stage.v ~5行代码 6. pipeline.v ~10行代码

#### ・课程作业情况

#### 关于 Debug

在你完成 CPU 实现后,运行测试程序将自动生成多个调试输出文件。每个文件提供不同层次的信息,帮助你理解 CPU 在每个周期做了什么,哪里可能出错了。

Tips: 假如你运行测试程序很久还没有输出,那很有可能是CPU死循环了,需要排查是否错误地发生了stall;

#### 输出文件说明

| 文件名格式                                           | 内容简介                                                                   |

|-------------------------------------------------|------------------------------------------------------------------------|

| <test_program.s>_detailed.csv</test_program.s>  | <b>每个周期各阶段的详细信号变化</b> (包括寄存器值、ALU输出、控制信号、PC等),适合深入单步追踪执行流程。            |

| <test_program.s>_memory.out</test_program.s>    | 程序运行结束后, <b>内存中数据的最终状态</b> 。                                           |

| <test_program.s>_pipeline.out</test_program.s>  | <b>流水线五个阶段在每个周期的执行情况</b> (即哪条指令在哪个阶段),尽管本 Lab 中是顺序<br>执行,也可用于观察执行是否正确。 |

| <test_program.s>_program.out</test_program.s>   | 仿真器的输出:辅助验证整体行为。                                                       |

| <test_program.s>_writeback.out</test_program.s> | 每次进入 WB 阶段时, <b>写回的寄存器编号、值和对应的 PC</b> 。                                |

你可以在 ./golden\_result 里面找到期望的输出,并用于参考;

#### ・课程作业情况

#### 关于 Debug

在你完成 CPU 实现后,运行测试程序将自动生成多个调试输出文件。每个文件提供不同层次的信息,帮助你理解 CPU 在每个周期做了什么,哪里可能出错了。

Tips: 假如你运行测试程序很久还没有输出,那很有可能是CPU死循环了,需要排查是否错误地发生了stall;

#### 输出文件说明

| 文件名格式                                           | 内容简介                                                                   |

|-------------------------------------------------|------------------------------------------------------------------------|

| <test_program.s>_detailed.csv</test_program.s>  | <b>每个周期各阶段的详细信号变化</b> (包括寄存器值、ALU输出、控制信号、PC等),适合深入单步追踪执行流程。            |

| <test_program.s>_memory.out</test_program.s>    | 程序运行结束后, <b>内存中数据的最终状态</b> 。                                           |

| <test_program.s>_pipeline.out</test_program.s>  | <b>流水线五个阶段在每个周期的执行情况</b> (即哪条指令在哪个阶段),尽管本 Lab 中是顺序<br>执行,也可用于观察执行是否正确。 |

| <test_program.s>_program.out</test_program.s>   | 仿真器的输出:辅助验证整体行为。                                                       |

| <test_program.s>_writeback.out</test_program.s> | 每次进入 WB 阶段时, <b>写回的寄存器编号、值和对应的 PC</b> 。                                |

你可以在 ./golden\_result 里面找到期望的输出,并用于参考;

・课程作业情况

- 1. 压缩为zip格式的实现的 Verilog 文件(提交整个 verilog/目录)你可以通过 make submit 来快速生成一个zip文件;

- 2. 简略的实验报告,包含:

- 实现思路

- 你调试时遇到的关键问题及解决方案

- 注意: 报告不超过 2 页

- 01. 超标量架构数据控制冲突

- 02. 动态发射与乱序执行设计

- 03. 分支处理机制与地址预测

- 04. 经典的MIPS架构实例分析

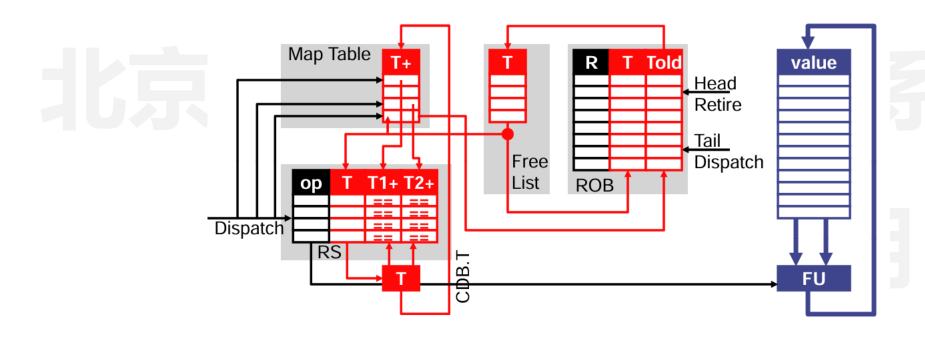

MIPS: An alternative implementation

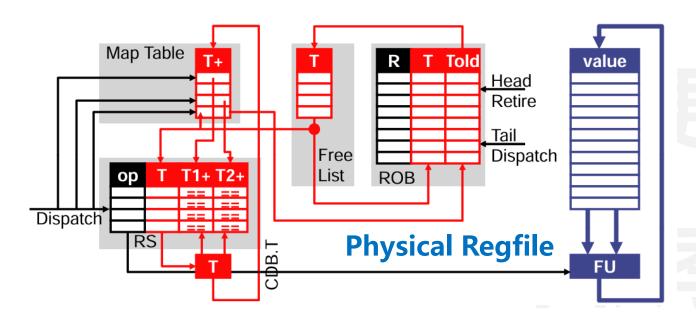

- · 一个大的物理寄存器堆保存所有数据-无需复制

- + 靠近 FU 的寄存器文件 → 小型快速数据路径 ROB

- ROB and RS "on the side" used only for control and tags

• MIPS: An alternative implementation

- · 架构寄存器文件? Gone

- 物理寄存器文件保存所有值

- #物理寄存器 = #架构寄存器+ #ROB entries

- 将架构寄存器映射到物理寄存器

- 消除数据冲突(物理寄存器取代 RS 副本)

- · 根本上改变 map table/RAT

- 映射不能为 0 (没有架构寄存器文件)

- 空闲列表跟踪未分配的物理寄存器

- · ROB 负责将物理寄存器返回到空闲列表

- 从概念上讲,这是"真正的寄存器重命名",因为没有寄存器值搬运

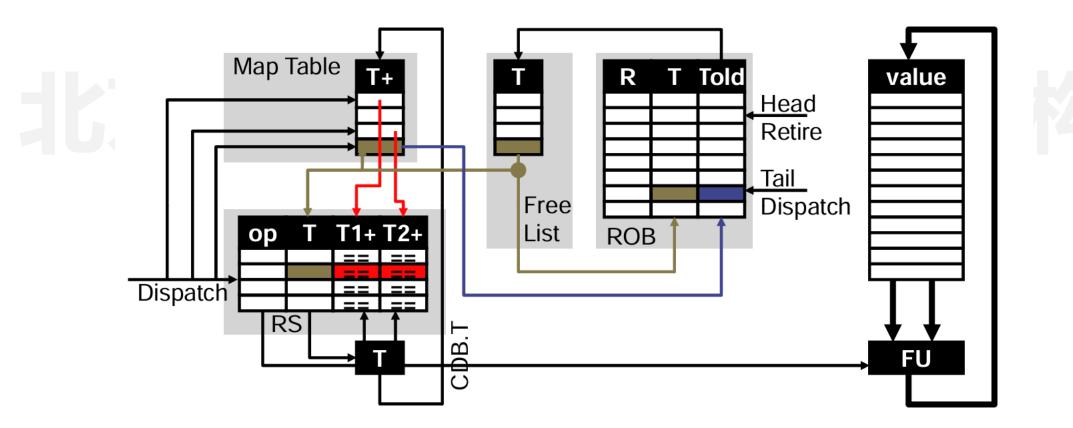

· MIPS R10K Dispatch步骤

- · T读取输入寄存器对应preg (物理寄存器)标签,存在RS

- Told: 之前映射到指令逻辑输出的物理寄存器读取输出寄存器的preg标签, 存在ROB (Told)

・MIPS R10K Complete步骤

- · 在map table中设定指令输出寄存器的ready bit

- 在RS中设定匹配输入标签的ready bits

· MIPS R10K Retire步骤

Return Told of ROB head to free list

思想自由 兼容并包 <12>

#### · MIPS实例分析

| RO | ROB |               |   |      |   |   |   |  |  |

|----|-----|---------------|---|------|---|---|---|--|--|

| ht | #   | Insn          | T | Told | S | X | С |  |  |

|    | 1   | 1df X(r1),f1  |   |      |   |   |   |  |  |

|    | 2   | mulf f0,f1,f2 |   |      |   |   |   |  |  |

|    | 3   | stf f2,Z(r1)  |   |      |   |   |   |  |  |

|    | 4   | addi r1,4,r1  |   |      |   |   |   |  |  |

|    | 5   | 1df X(r1),f1  |   |      |   |   |   |  |  |

|    | 6   | mulf f0,f1,f2 |   |      |   |   |   |  |  |

|    | 7   | stf f2,Z(r1)  |   |      |   |   |   |  |  |

| Мар  | Table   | CDB      |              |

|------|---------|----------|--------------|

| Reg  | T+      | T        |              |

| f0   | PR#1+   |          |              |

| f1   | PR#2+_  |          |              |

| f2   | PR#3+   |          |              |

| r1   | PR#4+   | <b>→</b> | ⊦: Ready bit |

| Free | List    | ·        | . I Cady bit |

| PR#  | 5,PR#6, |          |              |

| PR#  | 7, PR#8 |          |              |

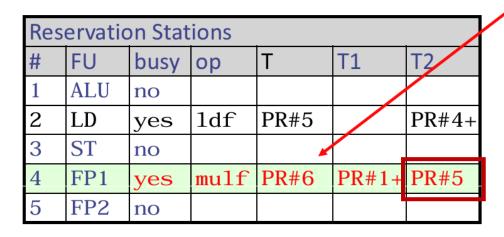

| Res | Reservation Stations |      |    |   |    |    |  |  |  |

|-----|----------------------|------|----|---|----|----|--|--|--|

| #   | FU                   | busy | ор | Т | T1 | T2 |  |  |  |

| 1   | ALU                  | no   |    |   |    |    |  |  |  |

| 2   | LD                   | no   |    |   |    |    |  |  |  |

| 3   | ST                   | no   |    |   |    |    |  |  |  |

| 4   | FP1                  | no   |    |   |    |    |  |  |  |

| 5   | FP2                  | no   |    |   |    |    |  |  |  |

Notice I: 任何地方都不存储寄存器values

Notice II: Map Table不为空

#### 和桌头掌 PEKING UNIVERSITY

#### · MIPS实例分析

| RO | В |               |      |      |   |   |   |

|----|---|---------------|------|------|---|---|---|

| ht | # | Insn          | Т    | Told | S | Χ | С |

| ht | 1 | 1df X(r1),f1  | PR#5 | PR#2 |   |   |   |

|    | 2 | mulf f0,f1,f2 |      | /    |   |   |   |

|    | 3 | stf f2,Z(r1)  |      |      |   |   |   |

|    | 4 | addi r1,4,r1  |      |      |   |   |   |

|    | 5 | 1df X(r1),f1  |      |      |   |   |   |

|    | 6 | mulf f0,f1,f2 |      |      |   | · | · |

|    | 7 | stf f2,Z(r1)  |      |      |   |   |   |

Map Table

Reg T+

f0 PR#1+

f1 PR#5

f2 PR#3+

r1 PR#4+

Free List

PR#5, PR#6,

PR#7, PR#8

#### MIPS:

### Cycle 1

| Res | Reservation Stations |      |     |      |      |       |  |  |  |

|-----|----------------------|------|-----|------|------|-------|--|--|--|

| #   | FU                   | busy | ор  | Т    | T1 / | 12    |  |  |  |

| 1   | ALU                  | no   |     |      |      |       |  |  |  |

| 2   | LD                   | yes  | 1df | PR#5 |      | PR#4+ |  |  |  |

| 3   | ST                   | no   |     |      |      |       |  |  |  |

| 4   | FP1                  | no   |     |      |      |       |  |  |  |

| 5   | FP2                  | no   |     |      |      |       |  |  |  |

给f1分配新的preg位置 (PR#5)

同时在ROB存储f1旧preg (PR#2)

CDB

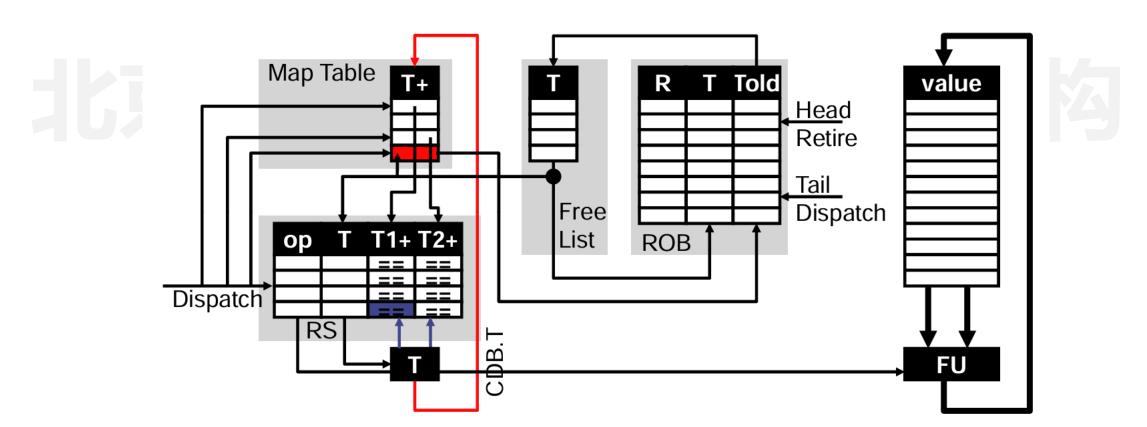

#### ・MIPS实例分析

| RO | ROB |               |      |      |    |   |   |  |  |

|----|-----|---------------|------|------|----|---|---|--|--|

| ht | #   | Insn          | Т    | Told | S  | Χ | С |  |  |

| h  | 1   | 1df X(r1),f1  | PR#5 | PR#2 | c2 |   |   |  |  |

| t  | 2   | mulf f0,f1,f2 | PR#6 | PR#3 |    |   |   |  |  |

|    | 3   | stf f2,Z(r1)  |      |      |    |   |   |  |  |

|    | 4   | addi r1,4,r1  |      |      |    |   |   |  |  |

|    | 5   | 1df X(r1),f1  |      |      |    |   |   |  |  |

|    | 6   | mulf f0,f1,f2 |      |      |    |   |   |  |  |

|    | 7   | stf f2,Z(r1)  |      |      |    |   |   |  |  |

Map Table

Reg T+

f0 PR#1+

f1 PR#5

f2 PR#6

r1 PR#4+

Free List

PR#6, PR#7,

PR#8

#### MIPS:

### Cycle 2

给f2分配新的preg位置 (PR#6)

同时在ROB存储f2旧preg (PR#3)

CDB

#### · MIPS实例分析

| RO | ROB |               |      |      |    |    |   |  |  |

|----|-----|---------------|------|------|----|----|---|--|--|

| ht | #   | Insn          | Т    | Told | S  | Χ  | C |  |  |

| h  | 1   | 1df X(r1),f1  | PR#5 | PR#2 | c2 | c3 |   |  |  |

|    | 2   | mulf f0,f1,f2 | PR#6 | PR#3 |    |    |   |  |  |

| t  | 3   | stf f2,Z(r1)  |      |      |    |    |   |  |  |

|    | 4   | addi r1,4,r1  |      |      |    |    |   |  |  |

|    | 5   | 1df X(r1),f1  |      |      |    |    |   |  |  |

| ·  | 6   | mulf f0,f1,f2 |      |      |    |    |   |  |  |

|    | 7   | stf f2,Z(r1)  |      |      |    |    |   |  |  |

| Map Table |       |  |  |  |  |

|-----------|-------|--|--|--|--|

| Reg       | T+    |  |  |  |  |

| f0        | PR#1+ |  |  |  |  |

| f1        | PR#5  |  |  |  |  |

| f2        | PR#6  |  |  |  |  |

| r1        | PR#4+ |  |  |  |  |

| Free L | ist  |

|--------|------|

| PR#7,  | PR#8 |

|        |      |

# MIPS:

### Cycle 3

**Reservation Stations** busy op # FU **T1** T2 **ALU** no LD no ST stf PR#6 PR#4+ ves mu1f PR#6 PR#1+ PR#5 FP1 yes FP2 no

Store指令不分配preg

Free 在X阶段即Free掉RS entry

思想自由 兼容并包 <16>

#### · MIPS实例分析

# MIPS:

## Cycle 4

| RO | ROB |               |      |      |            |    |            |  |  |

|----|-----|---------------|------|------|------------|----|------------|--|--|

| ht | #   | Insn          | Т    | Told | S          | Χ  | С          |  |  |

| h  | 1   | 1df X(r1),f1  | PR#5 | PR#2 | c2         | сЗ | <b>c</b> 4 |  |  |

|    | 2   | mulf f0,f1,f2 | PR#6 | PR#3 | <b>c</b> 4 |    |            |  |  |

|    | 3   | stf f2,Z(r1)  |      |      |            |    |            |  |  |

| t  | 4   | addi r1,4,r1  | PR#7 | PR#4 |            |    |            |  |  |

|    | 5   | 1df X(r1),f1  |      |      |            |    |            |  |  |

|    | 6   | mulf f0,f1,f2 |      |      |            |    |            |  |  |

|    | 7   | stf f2,Z(r1)  | -    |      |            |    |            |  |  |

| Reservation Stations |     |      |      |      |       |       |

|----------------------|-----|------|------|------|-------|-------|

| #                    | FU  | busy | ор   | Т    | T1    | T2    |

| 1                    | ALU | yes  | addi | PR#7 | PR#4+ |       |

| 2                    | LD  | no   |      |      |       |       |

| 3                    | ST  | yes  | stf  |      | PR#6  | PR#4+ |

| 4                    | FP1 | yes  | mu1f | PR#6 | PR#1+ | PR#5+ |

| 5                    | FP2 | no   |      |      |       |       |

| Map          | Table            | CDB  |

|--------------|------------------|------|

| Reg          | T+               | T    |

| f0           | PR#1+            | PR#5 |

| f1           | PR#5+            |      |

| f2           | PR#6             |      |

| r1           | PR#7             |      |

|              |                  | . \  |

| Free<br>PR#7 | List<br>7 , PR#8 |      |

Match PR#5 tag from CDB & issue

思想自由 兼容并包 < 17 >

#### · MIPS实例分析

| RO | В |               |      |      |    |    |    |

|----|---|---------------|------|------|----|----|----|

| ht | # | Insn          | Т    | Told | S  | Χ  | С  |

|    | 1 | 1df X(r1),f1  | PR#5 | PR#2 | с2 | с3 | c4 |

| h  | 2 | mulf f0,f1,f2 | PR#6 | PR#3 | С4 | c5 |    |

|    | 3 | stf f2,Z(r1)  |      |      |    |    | /  |

|    | 4 | addi r1,4,r1  | PR#7 | PR#4 | c5 |    |    |

| t  | 5 | 1df X(r1),f1  | PR#8 | PR#5 |    |    |    |

|    | 6 | mulf f0,f1,f2 |      |      |    |    |    |

|    | 7 | stf f2,Z(r1)  |      |      |    |    |    |

| Map | Table |

|-----|-------|

| Reg | T+    |

| f0  | PR#1+ |

| f1  | PR#8  |

| f2  | PR#6  |

| r1  | PR#7  |

Free List PR#8, PR#2

### MIPS:

### Cycle 5

| Res | Reservation Stations |      |      |      |       |       |

|-----|----------------------|------|------|------|-------|-------|

| #   | FU                   | busy | ор   | Т    | T1    | T2    |

| 1   | ALU                  | yes  | addi | PR#7 | PR#4+ |       |

| 2   | LD                   | yes  | 1df  | PR#8 |       | PR#7  |

| 3   | ST                   | yes  | stf  |      | PR#6  | PR#4+ |

| 4   | FP1                  | no   |      |      |       |       |

| 5   | FP2                  | no   |      |      |       |       |

Idf retires

Return PR#2 to free list

Free 在X阶段即Free掉RS entry

#### ・MIPS实例分析

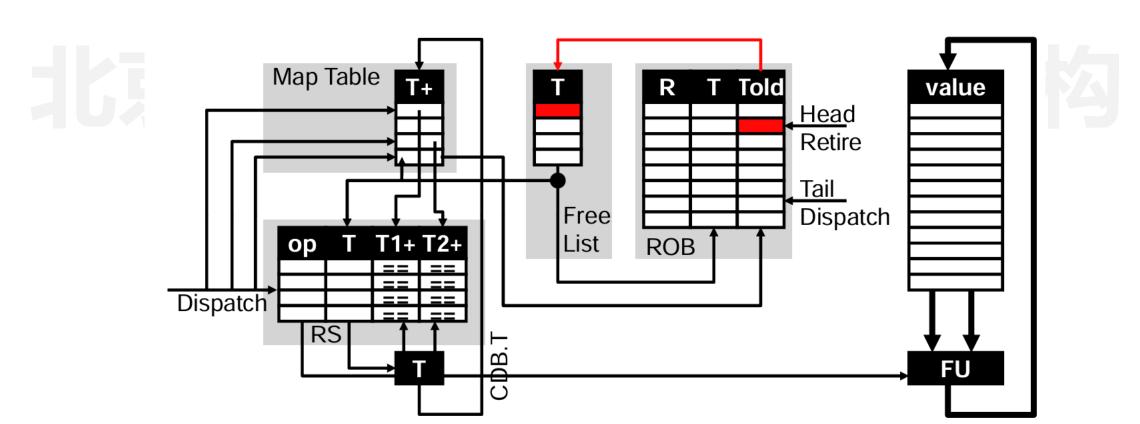

- Problem with R10K design? Precise state is more difficult

- -- 物理寄存器乱序写入

- 是可以的,没有架构寄存器文件

- · 我们可以 "free" 被写入的寄存器并 "restore" 旧的

- 通过控制Map Table和Free List来完成,而不是寄存器文件

- 两种恢复Map Table 和Free List的方式

- · 方式1: 通过用ROB中的T, Told串行恢复(速度慢但简单)

- · 方式2:从一些检查点单周期恢复(速度快,但检查点是昂贵的)

- 现代处理器的折中方案: 让普遍情况快速运行

- 需要频繁rollback的跳转使用检查点

- 较少rollback的Page-fault和interrupt进行串行恢复

#### ・MIPS实例分析

Replace with a taken branch

MIPS:

Cycle 5

**Precise**

**State**

| RO | В |               |      |      |    |    |    |

|----|---|---------------|------|------|----|----|----|

| ht | # | Insn          | Т    | Told | S  | Χ  | C  |

|    | 1 | 1df X(r1),f1  | PR#5 | PR#2 | c2 | c3 | c4 |

| h  | 2 | jmp f0 f1 f2  | PR#6 | PR#3 | c4 | c5 |    |

|    | 3 | stf f2,Z(r1)  |      |      |    |    |    |

|    | 4 | addi r1,4,r1  | PR#7 | PR#4 | c5 |    |    |

| t  | 5 | 1df X(r1),f1  | PR#8 | PR#5 |    |    |    |

|    | 6 | mulf f0,f1,f2 |      |      |    |    |    |

|    | 7 | stf f2,Z(r1)  |      |      |    |    |    |

| Map Table |       |  |

|-----------|-------|--|

| Reg       | T+    |  |

| f0        | PR#1+ |  |

| f1        | PR#8  |  |

| f2        | PR#6  |  |

| r1        | PR#7  |  |

Free List

PR#8, PR#2

| CDB | ) |

|-----|---|

| Т   |   |

|     |   |

| Reservation Stations |     |      |      |      |       |       |

|----------------------|-----|------|------|------|-------|-------|

| #                    | FU  | busy | ор   | T    | T1    | T2    |

| 1                    | ALU | yes  | addi | PR#7 | PR#4+ |       |

| 2                    | LD  | yes  | 1df  | PR#8 |       | PR#7  |

| 3                    | ST  | yes  | stf  |      | PR#6  | PR#4+ |

| 4                    | FP1 | no   |      |      |       |       |

| 5                    | FP2 | no   |      |      |       |       |

如果指令2采取跳转,则通 过rollback撤销指令3-5

思想自由 兼容并包 <20 >

#### は 対 は よ 対 PEKING UNIVERSITY

#### ・MIPS实例分析

| RO | В |               |      |      |    |    |    |

|----|---|---------------|------|------|----|----|----|

| ht | # | Insn          | Т    | Told | S  | Χ  | С  |

|    | 1 | 1df X(r1),f1  | PR#5 | PR#2 | c2 | сЗ | c4 |

| h  | 2 | jmp f0 f1 f2  | PR#6 | PR#3 | c4 | с5 |    |

|    | 3 | stf f2,Z(r1)  |      |      |    |    |    |

| t  | 4 | addi r1,4,r1  | PR#7 | PR#4 | c5 |    |    |

|    | 5 | 1df X(r1),f1  | PR#8 | PR#5 |    |    |    |

|    | 6 | mulf f0,f1,f2 |      |      |    |    |    |

|    | 7 | stf f2,Z(r1)  |      |      |    |    |    |

| Table |

|-------|

| T+    |

| PR#1+ |

| PR#5+ |

| PR#6  |

| PR#7  |

|       |

| CDB |

|-----|

| Т   |

|     |

MIPS:

Cycle 6

| Res | Reservation Stations |      |      |      |       |       |  |

|-----|----------------------|------|------|------|-------|-------|--|

| #   | FU                   | busy | ор   | Т    | T1    | T2    |  |

| 1   | ALU                  | yes  | addi | PR#7 | PR#4+ |       |  |

| 2   | LD                   | no   |      |      |       |       |  |

| 3   | ST                   | yes  | stf  |      | PR#6  | PR#4+ |  |

| 4   | FP1                  | no   |      |      |       |       |  |

| 5   | FP2                  | no   |      |      |       |       |  |

#### 撤销ldf (ROB#5)

Free List

PR#2, PR#8

- 1.释放RS

- 2.释放T (PR#8) ,返回Freelist

- 3.将MT[f1]重新存储到Told (PR#5)

- 4.释放ROB#5

指令可以rollback执行

#### ・MIPS实例分析

#### **ROB** ht |# |Insn Told S X 1df X(r1), f1PR#5 PR#2 c2c3c4PR#6 PR#3 jmp f0 f1 f2 c4c5 $3 \mid stf f2, Z(r1)$ PR#7 PR#4 c5 4 addi r1,4,r1 1df X(r1), f1 mulf f0, f1, f2 stf f2,Z(r1)

| Map Table |       |  |  |  |  |

|-----------|-------|--|--|--|--|

| Reg       | T+    |  |  |  |  |

| f0        | PR#1+ |  |  |  |  |

| f1        | PR#5+ |  |  |  |  |

| f2        | PR#6  |  |  |  |  |

| r1        | PR#4+ |  |  |  |  |

### MIPS:

#### Cycle 7

| Res | Reservation Stations |      |     |   |      |       |  |

|-----|----------------------|------|-----|---|------|-------|--|

| #   | FU                   | busy | ор  | Т | T1   | T2    |  |

| 1   | ALU                  | no   |     |   |      |       |  |

| 2   | LD                   | no   |     |   |      |       |  |

| 3   | ST                   | yes  | stf |   | PR#6 | PR#4+ |  |

| 4   | FP1                  | no   |     |   |      |       |  |

| 5   | FP2                  | no   |     |   |      |       |  |

#### 撤销ldf (ROB#4)

PR#2, PR#8,

Free List

1.释放RS

PR#7

- 2.释放T (PR#7) ,返回Freelist

- 3.将MT[r1]重新存储到Told (PR#4)

- 4.释放ROB#4

#### · MIPS实例分析

| RO | В |               |      |      |    |    |    |

|----|---|---------------|------|------|----|----|----|

| ht | # | Insn          | Т    | Told | S  | Χ  | С  |

|    | 1 | 1df X(r1),f1  | PR#5 | PR#2 | c2 | сЗ | c4 |

| ht | 2 | jmp f0 f1 f2  | PR#6 | PR#3 | c4 | с5 |    |

|    | 3 | stf f2,Z(r1)  |      |      |    |    |    |

|    | 4 | addi r1,4,r1  |      |      |    |    |    |

|    | 5 | 1df X(r1),f1  |      |      |    |    |    |

|    | 6 | mulf f0,f1,f2 |      |      |    |    |    |

|    | 7 | stf f2,Z(r1)  |      |      |    |    |    |

| Map Table |       |  |  |  |  |

|-----------|-------|--|--|--|--|

| Reg       | T+    |  |  |  |  |

| f0        | PR#1+ |  |  |  |  |

| f1        | PR#5+ |  |  |  |  |

| f2        | PR#6  |  |  |  |  |

| r1        | PR#4+ |  |  |  |  |

|           |       |  |  |  |  |

| CDB |  |

|-----|--|

| Т   |  |

|     |  |

Free List PR#2, PR#8, PR#7

#### MIPS:

### Cycle 8

| Res | Reservation Stations |      |    |   |    |    |  |

|-----|----------------------|------|----|---|----|----|--|

| #   | FU                   | busy | ор | Т | T1 | T2 |  |

| 1   | ALU                  | no   |    |   |    |    |  |

| 2   | LD                   | no   |    |   |    |    |  |

| 3   | ST                   | no   |    |   |    |    |  |

| 4   | FP1                  | no   |    |   |    |    |  |

| 5   | FP2                  | no   |    |   |    |    |  |

#### 撤销ldf (ROB#3)

- 1.释放RS

- 2.释放ROB#3

- 3.没有寄存器需要恢复/释放

- 4.D\$的写入如何撤销?

思想自由 兼容并包 <23>

- 01. 动态发射与乱序执行设计

- 02. 分支处理机制与地址预测

- 03. 经典的MIPS架构实例分析

- 04. 多级缓存微架构与一致性

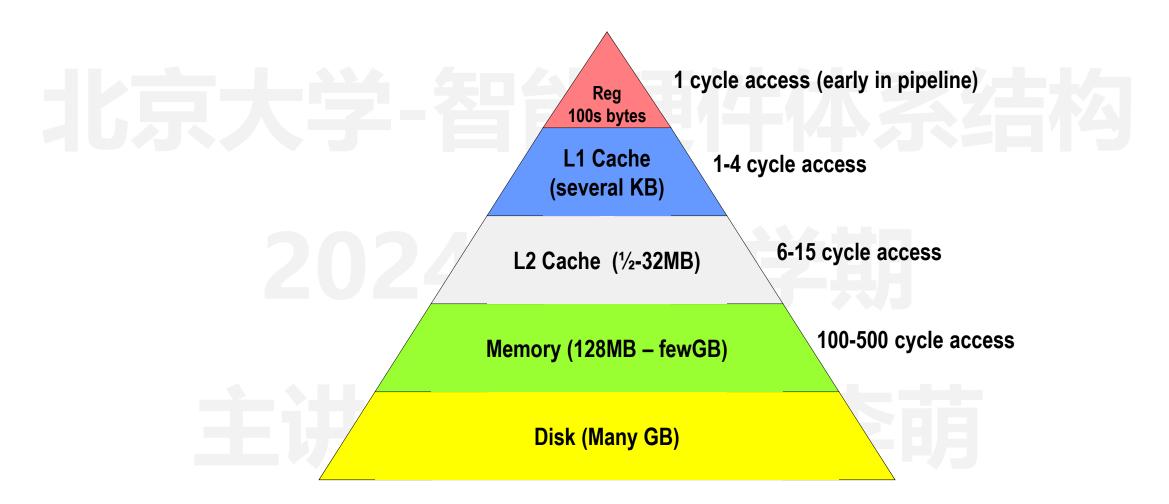

### 缓存Cache设计基础

・当前芯片架构中的缓存层级

### 缓存Cache设计中的局部性

- · 局部性原理 时间局部性与空间局部性

- 局部性原理:

- 程序倾向于重复使用最近使用过的数据和指令。

- 时间局部性: 最近引用的项目很可能在不久的将来被引用。

- 空间局部性: 地址相近的物品往往会在时间上被紧密引用。

### 示例中的局部性:

- 数据

- -连续引用数组元素(空间)

- 指令

- -按顺序(空间)引用指令

- 反复循环 (时间)

```

sum = 0;

for (i = 0; i < n; i++)

sum += a[i];

*v = sum;

```

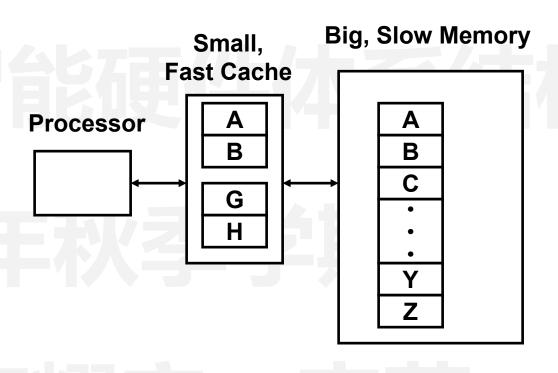

#### ・加快访存速度

#### Main Memory

Stores words

A–Z in example

#### Cache

- Stores subset of the words

4 in example

- Organized in lines

- Multiple words

- To exploit spatial locality

#### Access

Word must be in cache for processor to access

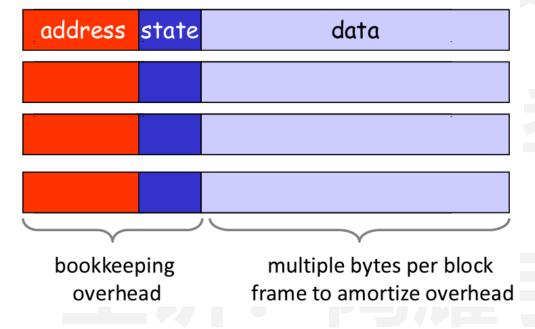

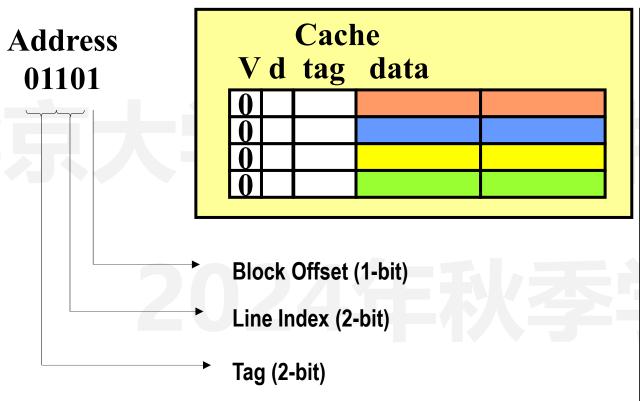

#### · Cache的抽象模型

Keep recently accessed block in "block frame"

- state (e.g., valid)

- address tag

- data

#### On memory read

- if incoming address corresponds to on e of the stored address tag then

- HIT

- return data

- else

- MISS

- Choose and displace a current block in use

- fetch new (referenced) block from memory into frame

- return data

#### · Cache使用术语

- block (cache line) minimum unit that may be present

- hit block is found in the cache

- miss —block is not found in the cache

- miss ratio fraction of references that miss

- hit time —time to access the cache miss penalty

- miss penalty

- time to replace block in the cache + deliver to upper level

- access time time to get first word

- transfer time time for remaining words

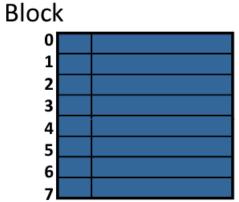

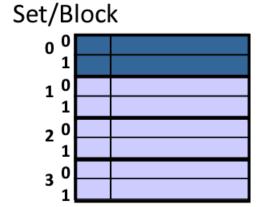

#### Cache Block Placement

Where does block 12 (b'1100) go?

<u>Fully-associative</u> block goes in any frame Set-associative

a block goes in any

frame in exactly one set

<u>Direct-mapped</u> block goes in exactly one frame

(think all frames in 1 set)

(frames grouped into sets)

(think 1 frame per set)

#### Cache Block Size的概念

- Each cache block frame or (cache line) has only one tag but can hold multiple "chunks" of data

- Reduce tag storage overhead

- In 32-bit addressing, an 1-MB direct-mapped cache has 12 bits of tags

- 4-byte cache block ⇒ 256K blocks ⇒ ~384KB of tag

- 128-byte cache block ⇒ 8K blocks ⇒ ~12KB of tag

- The entire cache block is transferred to and from memory all at once

- good for spatial locality because if you access address i you will probably want i+1 as well (prefetching effect)

- Block size = 2<sup>h</sup>; Direct Mapped Cache Size = 2<sup>h</sup>(B+b)

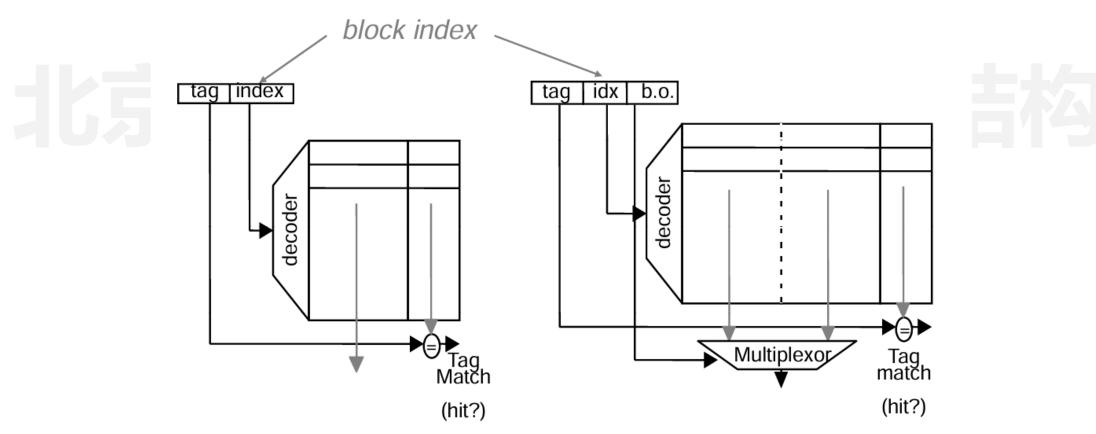

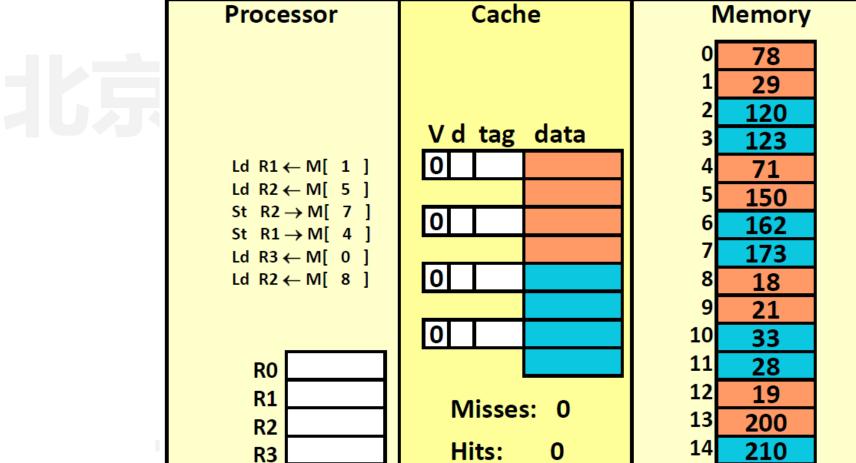

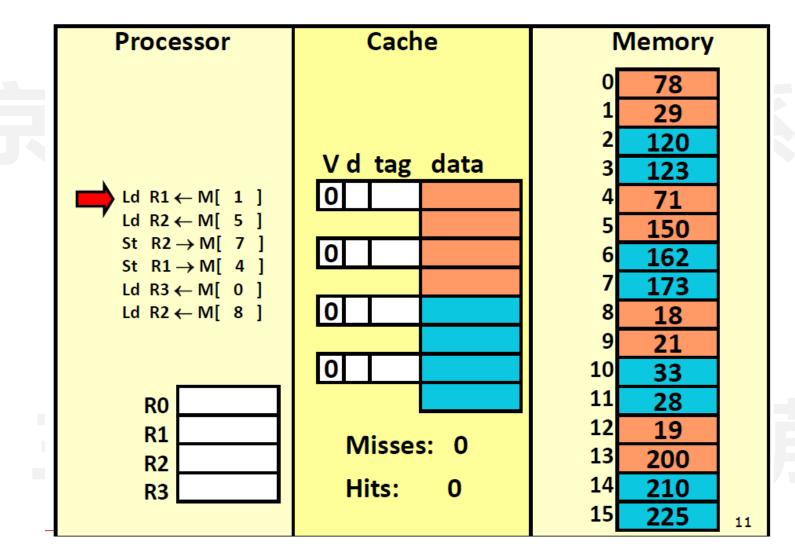

### Direct-Mapped Cache设计

| Memory               |     |     |  |  |  |  |

|----------------------|-----|-----|--|--|--|--|

| 00000                | 78  | 23  |  |  |  |  |

| 00010                | 29  | 218 |  |  |  |  |

| 00100                | 120 | 10  |  |  |  |  |

| 00110                | 123 | 44  |  |  |  |  |

| 01000                | 71  | 16  |  |  |  |  |

| 01010                | 150 | 141 |  |  |  |  |

| 01100                | 162 | 28  |  |  |  |  |

| 01110                | 173 | 214 |  |  |  |  |

| 10000                | 18  | 33  |  |  |  |  |

| 10010                | 21  | 98  |  |  |  |  |

| 10 <mark>10</mark> 0 | 33  | 181 |  |  |  |  |

| 10110                | 28  | 129 |  |  |  |  |

| 11000                | 19  | 119 |  |  |  |  |

| 11010                | 200 | 42  |  |  |  |  |

| 11100                | 210 | 66  |  |  |  |  |

| 11110                | 225 | 74  |  |  |  |  |

|                      |     |     |  |  |  |  |

#### 3-C's

**Compulsory Miss:** first reference to memory block

**Capacity Miss:** Working set doesn't fit in cache

**Conflict Miss:** Working set maps to same cache line

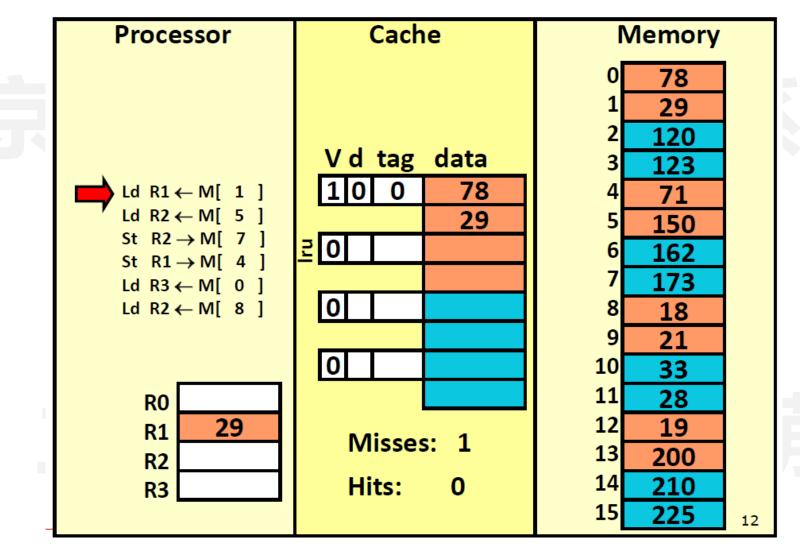

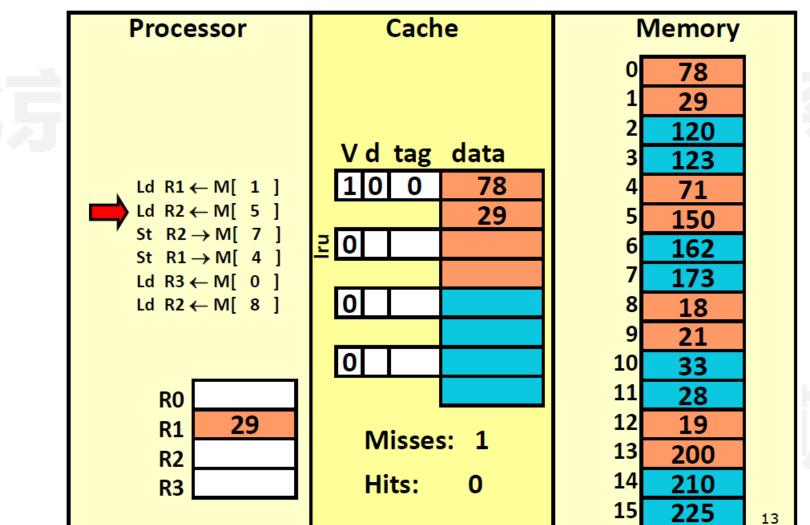

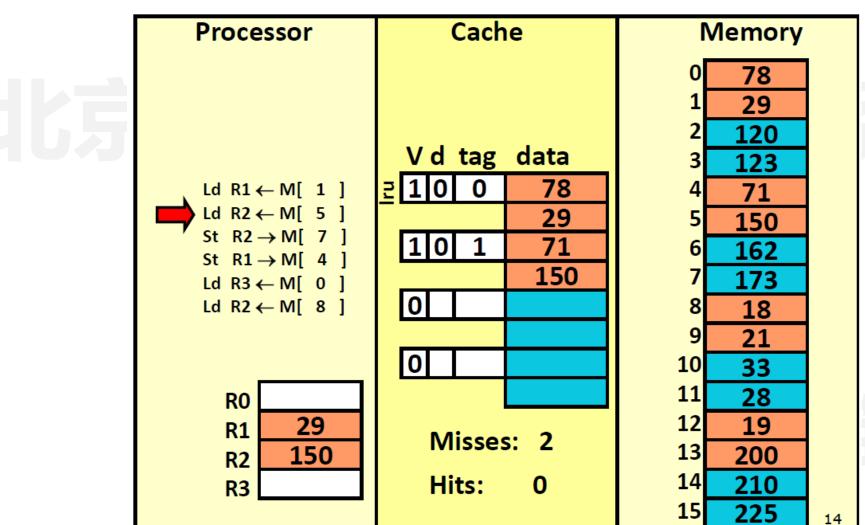

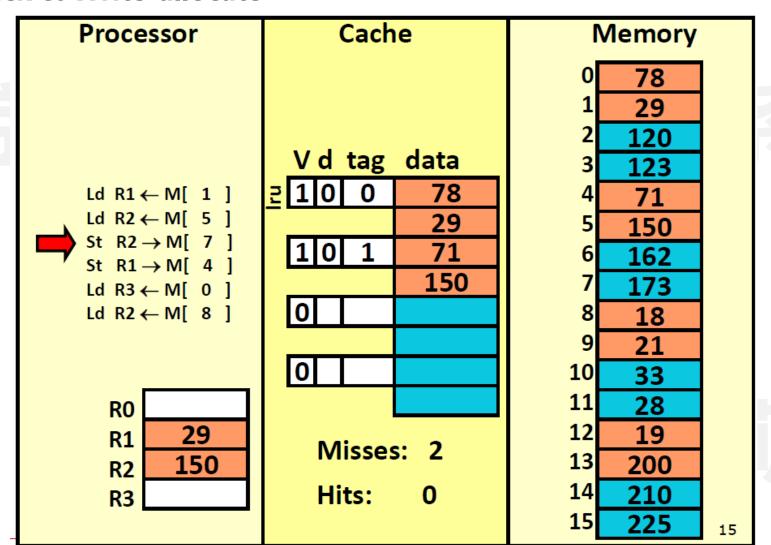

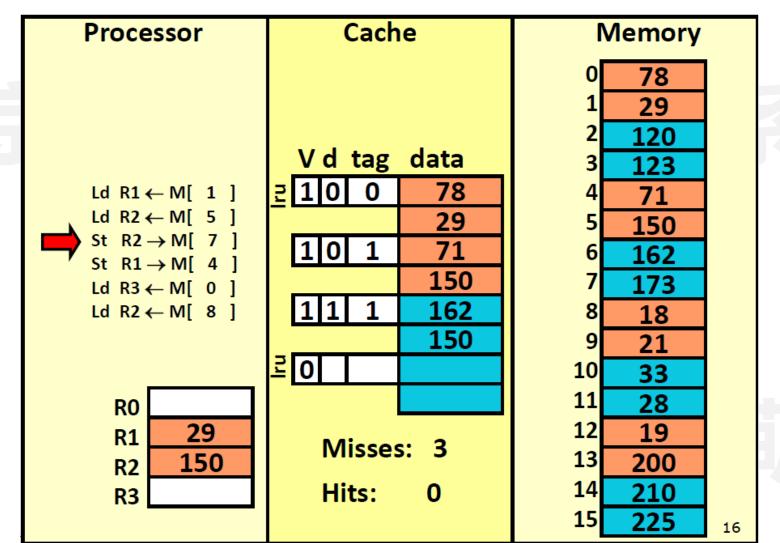

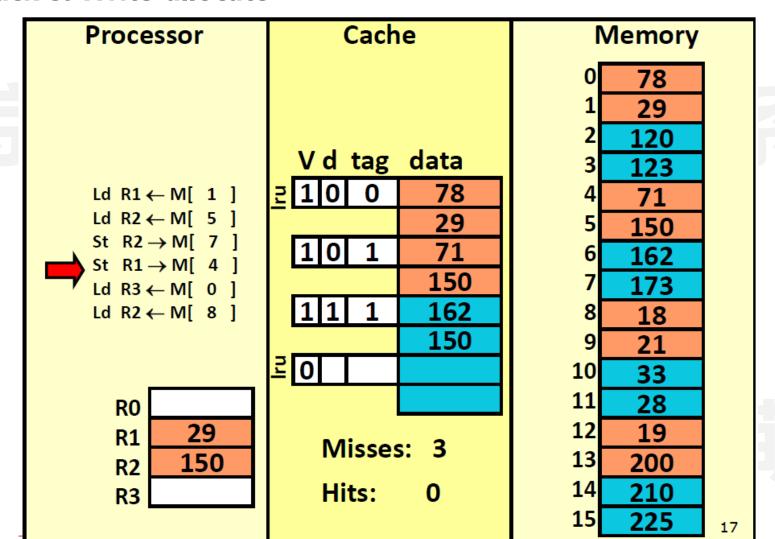

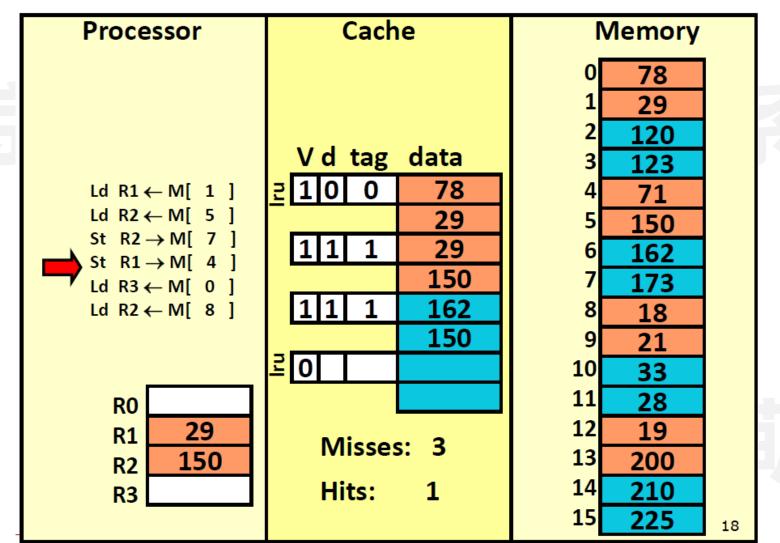

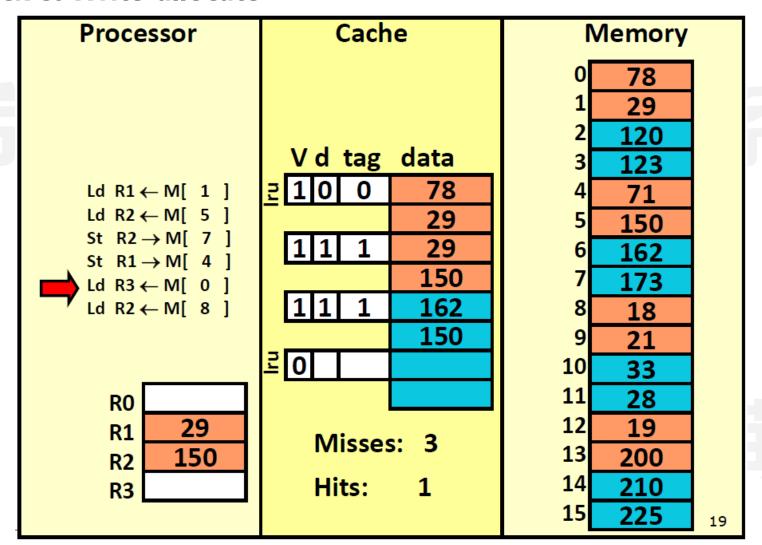

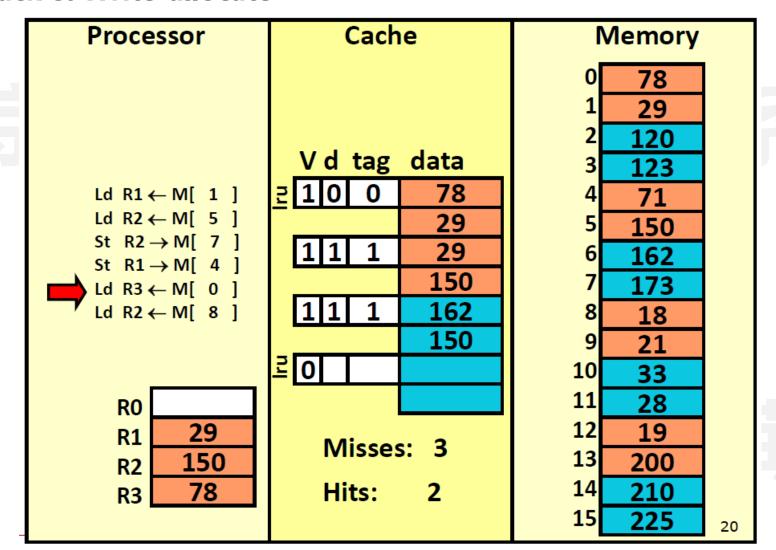

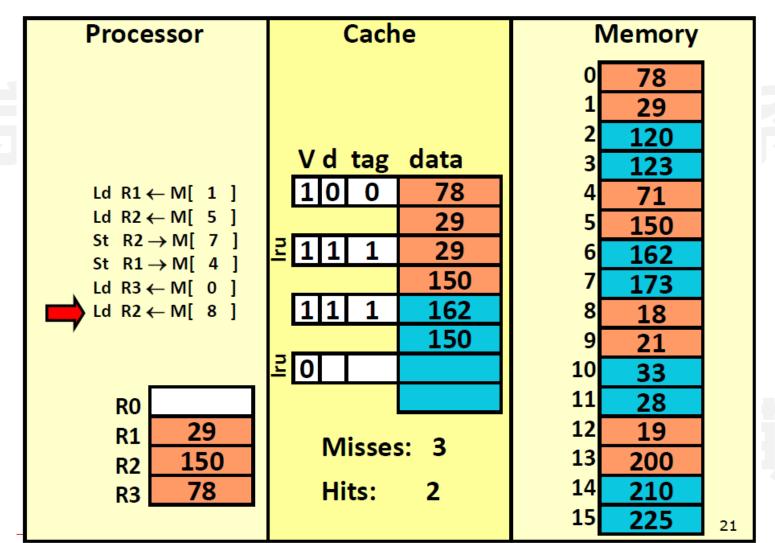

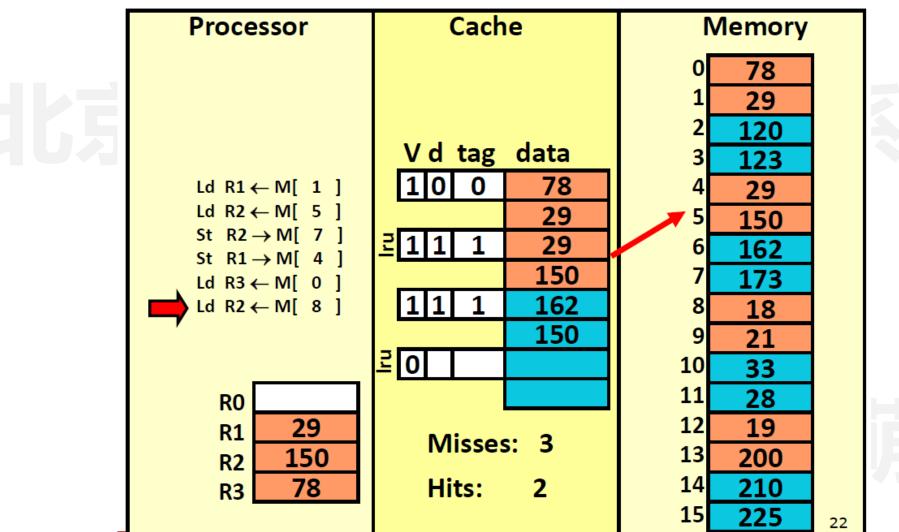

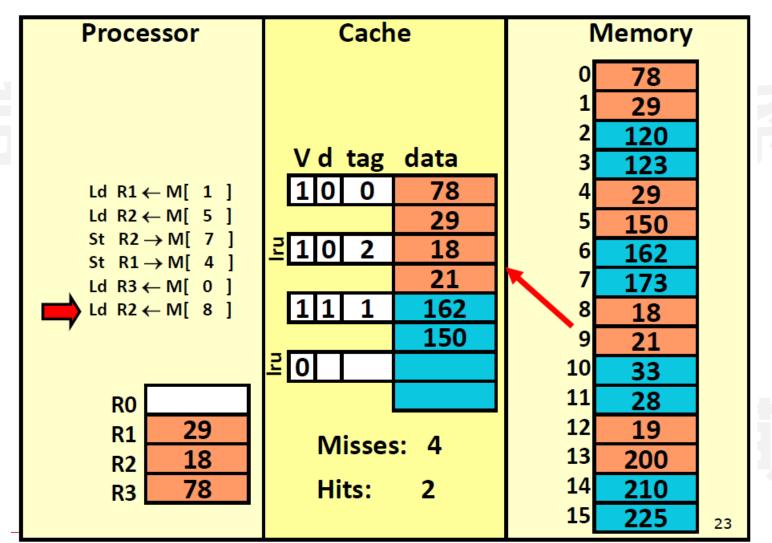

### Direct-Mapped Cache设计

Don't forget to check the valid/state bits

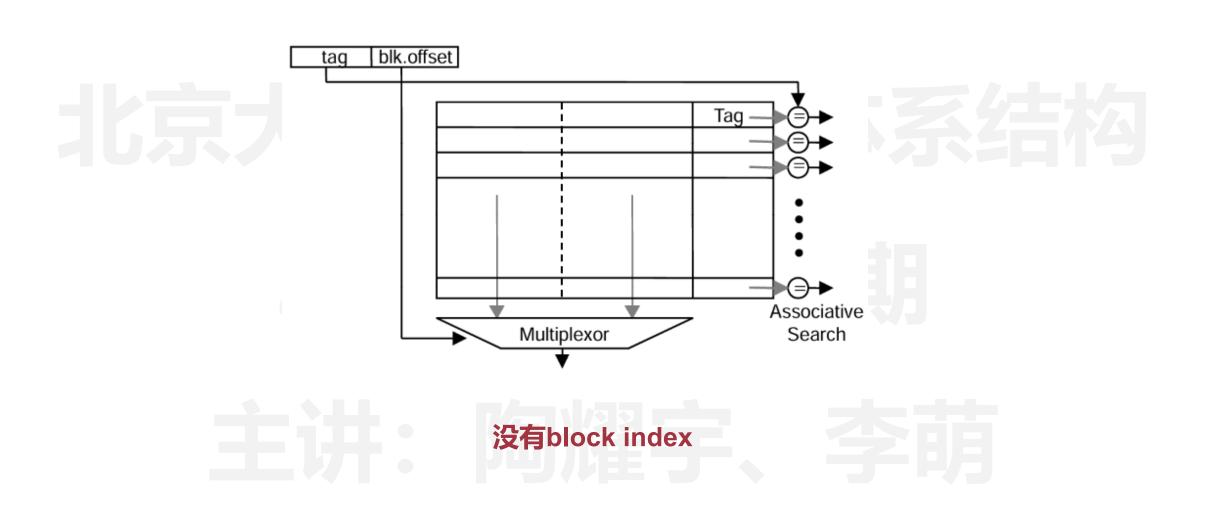

### Fully-Associative Cache设计

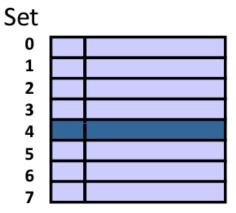

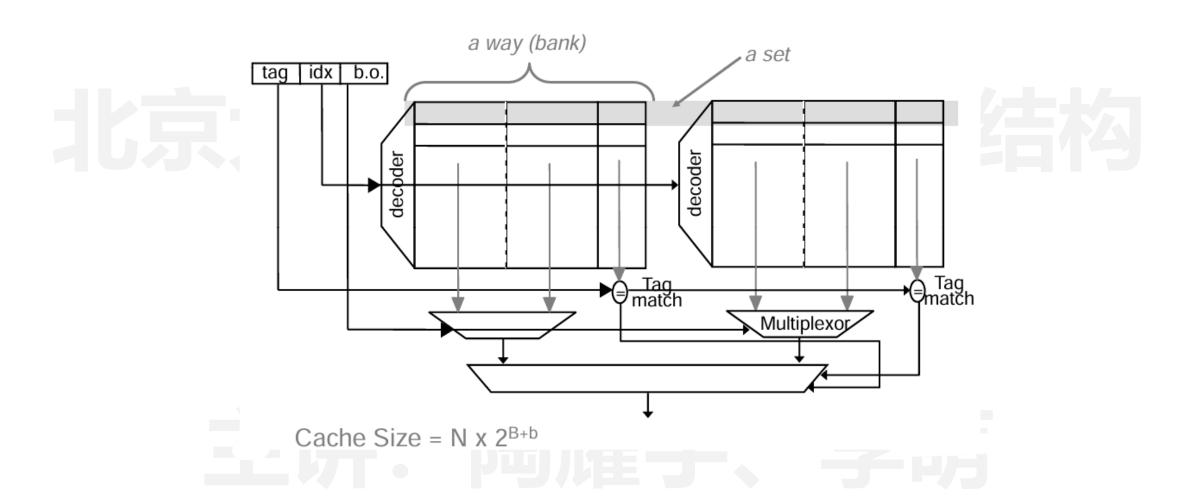

### N-Way Set Associative Cache设计

### N-Way Set Associative Cache设计

- Associative Block Replacement

- 当发生未命中时要替换set中的哪一个block?

- 理想情况下 — 替换未来最晚被访问的block

- 如何实现?

- Approximations:

- Least recently used LRU

- 针对时间局部性进行了优化 (假设有的话), 对于超过两路的情况, 成本较高

- Not most recently used NMRU

- 跟踪 MRU, 从其他block中随机选择, 很好的折衷方案

- Random

- · 几乎和 LRU 一样好,更简单(通常是伪随机)

- 区块替换政策有多重要?

## Cache Miss种类

- Miss Classification (3+1 C's)

- Compulsory Miss

- · 首次访问某个块时出现 "cold miss"

- defined as: miss in infinite cache

- Capacity Miss

- 由于缓存不够大而发生未命中—

defined as: miss in fully-associative cache

- Conflict Miss

- 由于限制性映射策略而发生未命中

- 仅在组相联或直接映射缓存中

- defined as: not attributable to compulsory or capacity

- Coherence Miss

- ・由于多处理器之间的共享而发生未命中

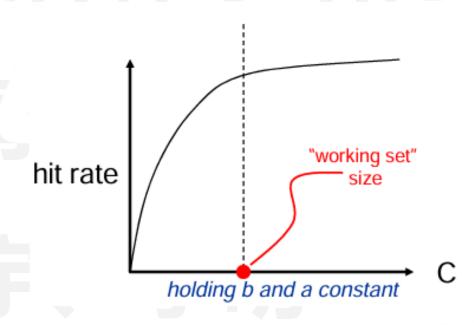

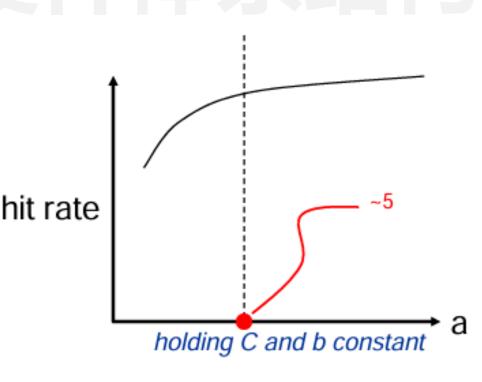

## Cache参数的选择

Cache Size (C) , Block Size (b) , Associativity (a)

# ・ 缓存大小是总数据 (不包括标签) 容量

- 更大可以更好地利用时间局部性

- not ALWAYS better

### ・缓存太大

- 越小越快 => 越大越慢

- 访问时间可能会降低关键路径

## ・缓存太小

- 没有很好地利用时间局部性

- 有用的数据不断被替换

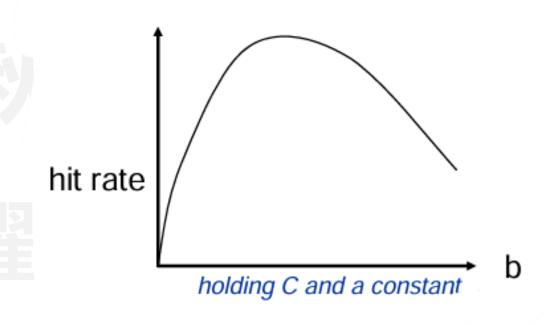

## Cache参数的选择

### • Block Size (b)

## ・块大小是指

- 与地址标签关联

- 不一定是层次结构之间的传输单位 (remember sub-blocking)

## ・区块太小

- 没有很好地利用空间局部性

- 有过多的标签开销

## ・块太大

- 传输了无用的数据

- 有用数据被频繁替换

- 总区块数太少

## Cache参数的选择

- Associativity (a)

- Partition cache frames into

- equivalence classes of frames called sets

- Typical values for associativity

- 1, 2-, 4-, 8-路相关

- Larger associativity

- 更低的miss rate可以减小程序的变动

- 仅对小"C/b"重要

- Smaller associativity

- 成本更低,命中时间更快

## Cache设计选择的影响

- · Cache写入和Miss处理策略

- 写入策略: 如何处理写入未命中?

- Write-through / no-allocate

- 每次写入时更新内存

- 保持内存更新

- Write-back / write-allocate

- 仅在块替换时更新内存

- 许多缓存行只读,从不写入

- 将"dirty"位添加到状态字

- 替换后原先清除

- · 当块帧被写入时set

- 仅写回dirty块,并清除clean块而不进行内存更新

| Memory         |     |     |  |  |  |  |

|----------------|-----|-----|--|--|--|--|

| 00000          | 78  | 23  |  |  |  |  |

| 00010          | 29  | 218 |  |  |  |  |

| 00100          | 120 | 10  |  |  |  |  |

| 00110          | 123 | 44  |  |  |  |  |

| 01000          | 71  | 16  |  |  |  |  |

| 01010          | 150 | 141 |  |  |  |  |

| 01100          | 162 | 28  |  |  |  |  |

| 01110          | 173 | 214 |  |  |  |  |

| 10000          | 18  | 33  |  |  |  |  |

| 10010          | 21  | 98  |  |  |  |  |

| 10100          | 33  | 181 |  |  |  |  |

| 10110          | 28  | 129 |  |  |  |  |

| 11000          | 19  | 119 |  |  |  |  |

| <b>11010</b>   | 200 | 42  |  |  |  |  |

| 111 <b>0</b> 0 | 210 | 66  |  |  |  |  |

| 11110          | 225 | 74  |  |  |  |  |

Write-back & Write-allocate

225

10

Write-back & Write-allocate

Write-back & Write-allocate

Write-back & Write-allocate

Write-back & Write-allocate

Write-back & Write-allocate

## 案例分析

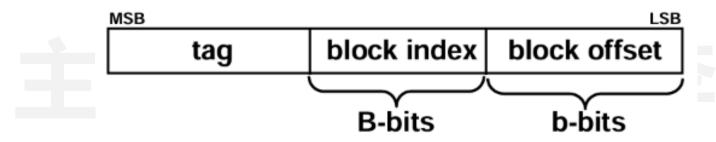

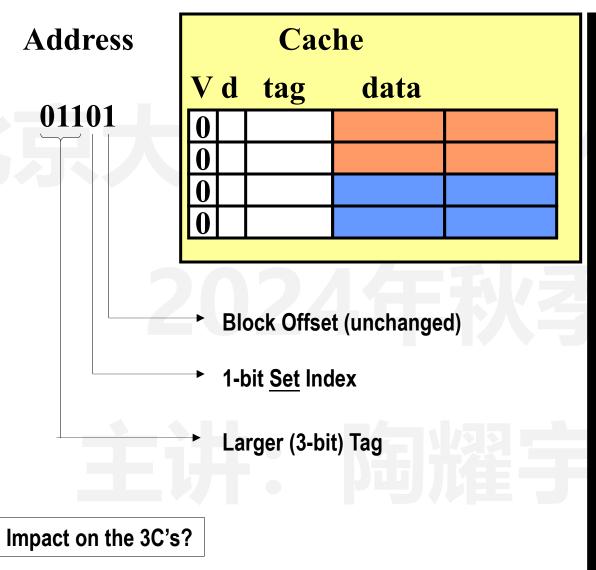

#### · Cache地址的比特分区映射

对于 32 位地址和具有 64 字节block的 16KB 缓存,不同缓存配置的地址breakdown:

#### A) fully associative cache

Block Offset = 6 bits Tag = 32 - 6 = 26 bits

#### C) Direct-mapped cache

Block Offset = 6 bits #lines = 256 Line Index = 8 bits Tag = 32 - 6 - 8 = 18 bits

#### B) 4-way set associative cache

Block Offset = 6 bits #sets = #lines / ways = 64 Set Index = 6 bits Tag = 32 - 6 - 6 = 20 bits

## 案例分析

- · Cache Access时间分析

- T\_avg = T\_hit + miss\_ratio x T\_miss

- comparable DM and SA caches with same T\_miss

- 但是最小化T\_avg的associativity一般比最小化miss\_ratio 的associativity要小

$$diff(t_{cache}) = t_{cache}(SA) - t_{cache}(DM) \ge 0$$

$diff(miss) = miss(SA) - miss(DM) \le 0$

e.g., assuming diff(t<sub>cache</sub>)= 0 => SA better

assuming diff(miss) = -1%,

$$t_{miss}$$

= 20

$\Rightarrow$  if diff( $t_{cache}$ ) > 0.2 cycle then SA loses

- 01. 动态发射与乱序执行回顾

- 02. 多级缓存微架构设计原理

- 03. 多级缓存的一致性机制

- 04. 缓存设计的优化方向

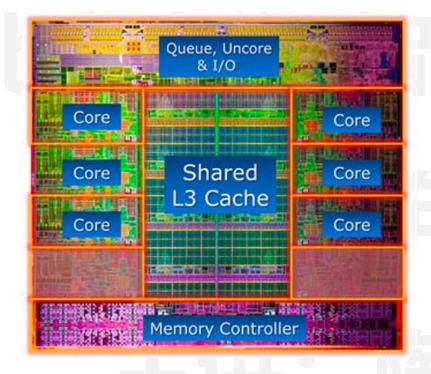

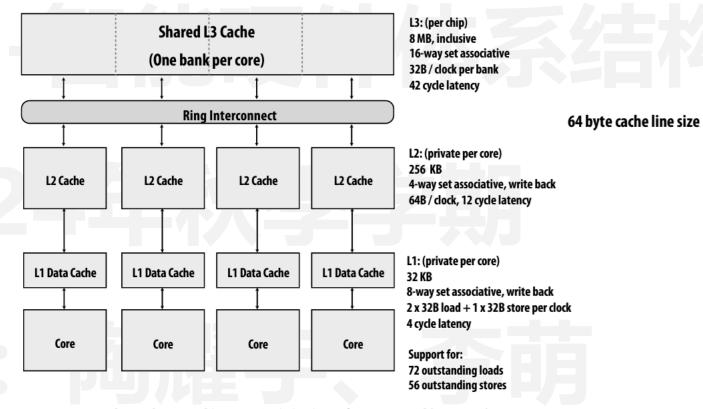

・多核共享cache

#### Intel® Core™ i7-3960X Processor Die Detail

■ 30% of the die area is cache

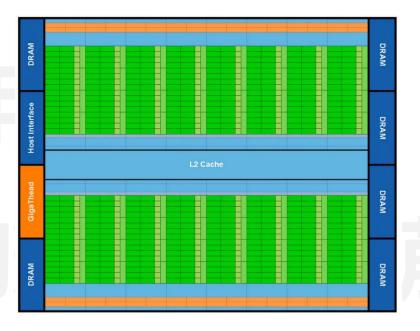

Nvidia GPU Architecture

#### 和某人学 PEKING UNIVERSITY

### ・多核共享cache

#### **Caches exploit locality**

#### 3 Cs cache miss model

- Cold

- Capacity

- Conflict

Source: Intel 64 and IA-32 Architectures Optimization Reference Manual (June 2016)

思想自由 兼容并包 <61>

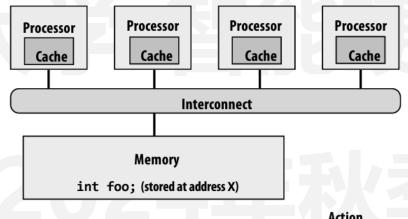

・多核共享cache

### 现代处理器在局部缓存中复制存储器的内容 问题:不同的处理器在同样内存位置可能会观察到不同的值

The chart at right shows the value of variable foo (stored at address X) in main memory and in each processor's cache

Assume the initial value stored at address X is 0

Assume write-back cache behavior

| Action     | P1 \$      | P2 \$ | P3 \$ P4 \$ | mem[X] |

|------------|------------|-------|-------------|--------|

|            |            |       |             | 0      |

| P1 load X  | 0 mi       | ss    |             | 0      |

| P2 load X  | 0          | 0 mi  | ss          | 0      |

| P1 store X | 1          | 0     |             | 0      |

| P3 load X  | 1          | 0     | 0 miss      | 0      |

| P3 store X | 1          | 0     | 2           | 0      |

| P2 load X  | 1          | 0 hi  | t 2         | 0      |

| P1 load Y  | causes evi | 0     | 2           | 1      |

(assume fully load fanses exittio

- ・缓存一致性协议

- 每个处理器的缓存控制器应该响应以下操作:

- -本地处理器Loads and stores

- -来自总线上其他缓存的消息

- 如果所有缓存控制器都按照所述协议运行, 那么将保持一致性

- - 缓存"合作"以确保保持一致性

- Invalidation-based write-back protocol

- ・ 关键思想:

- 处于 "已修改" 状态的行可以在不通知其他缓存的情况下进行修改

- ・处理器只能写入已修改状态的行

- 需要一种方法来告诉其他缓存,处理器想要独占访问该行

- 我们通过向所有其他缓存发送消息来实现这一点

- 当缓存控制器看到对其所包含的行进行修改访问的请求时

- 它必须使缓存中的行无效

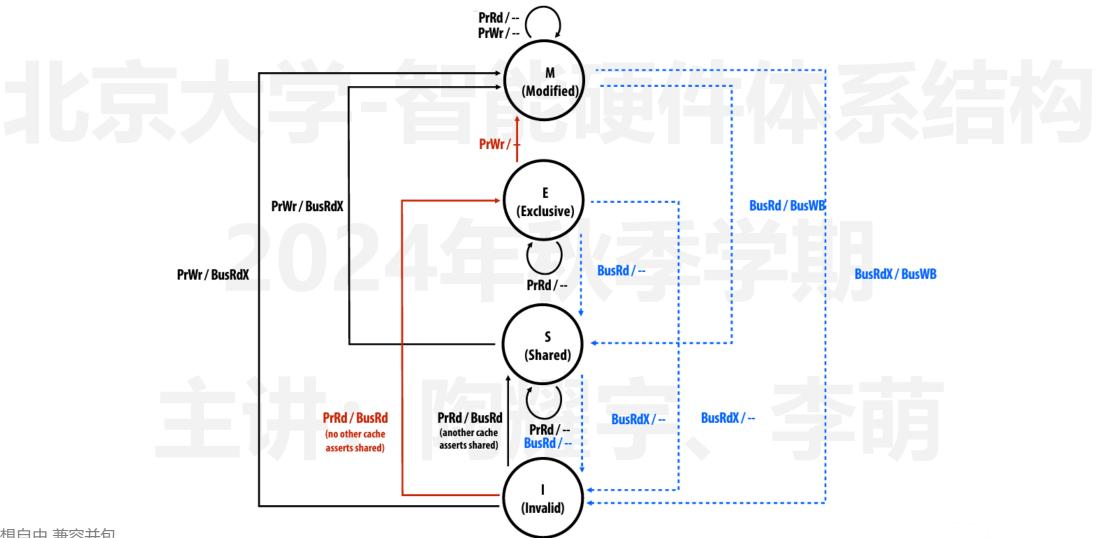

- MSI write-back invalidation protocol

- · 协议的主要任务

- 确保处理器获得写入的独占访问权限

- 在缓存未命中时查找缓存行数据的最新副本

- · 三种缓存行状态

- 无效(I):与单处理器缓存中的无效含义相同

- 共享(S): 行在一个或多个缓存中有效, 内存是最新的

- 已修改 (M): 仅在一个缓存中有效的行(又称 "dirty" 或 "exclusive" 状态)

- ・ 两个处理器操作 (由本地 CPU 触发)

- PrRd(读取)

- PrWr(写入)

- · 三个与一致性相关的总线操作 (来自远程缓存)

- BusRd: 获取缓存行副本, 无意修改

- · BusRdX: 获取要修改的缓存行副本

- BusWB:将dirty行写入内存

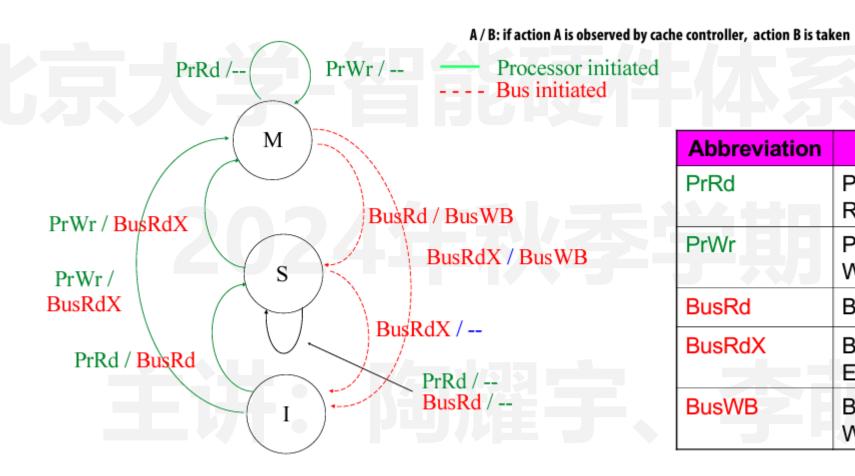

#### · Cache Coherence Protocol: MSI 状态图

| Abbreviation | Action                |  |

|--------------|-----------------------|--|

| PrRd         | Processor<br>Read     |  |

| PrWr         | Processor<br>Write    |  |

| BusRd        | Bus Read              |  |

| BusRdX       | Bus Read<br>Exclusive |  |

| BusWB        | Bus<br>Writeback      |  |

思想自由 兼容并包 < 66 >

Cache Coherence Protocol: MSI State Diagram

| <b>Proc Action</b> | P1 State | P2 state | P3 state | Bus Act D | ata from   |

|--------------------|----------|----------|----------|-----------|------------|

| 1. P1 read x       | S        |          |          | BusRd     | Memory     |

| 2. P3 read x       | S        |          | S        | BusRd     | Memory     |

| 3. P3 write x      |          |          | M        | BusRdX    | Memory     |

| 4. P1 read x       | S        |          | S        | BusRd     | P3's cache |

| 5. P2 read x       | S        | S        | S        | BusRd     | Memory     |

| 6. P2 write x      | 1        | M        | I        | BusRdX    | Memory     |

|                    |          |          |          |           |            |

- Cache Coherence Protocol: MESI invalidation protocol

- · 对于读取地址然后写入地址的常见情况,MSI 需要两个互联操作

- 操作 1: BusRd 把 I 状态转为 S 状态

- 操作 2: BusRdX 把 S 状态转为 M 状态

- · 即使应用程序根本没有共享,这种低效率仍然存在

- ・ 解决方案:添加附加状态 E( "exclusive clean" )

- 行未被修改,但只有此缓存有该行的副本

- 将exclusivity与行所有权分离(线路不脏,因此内存中的副本是数据的有效副本)

- 从 E 升级到 M 不需要总线操作

Cache Coherence Protocol: MESI invalidation protocol